XSG Utils Library

Ready-to-use fixed-point and floating-point function blocks for faster implementation of FPGA models

The XSG Utils Library offers ready-to-use function blocks for rapid control prototyping (RCP) or hardware-in-the-loop (HIL) simulation projects. The library gives users of real-time FPGA applications enhanced function blocks for implementing their own projects.

-

Completely open models for Simulink® and

Xilinx® Vitis™ Model Composer HDL Library, the former Xilinx® System Generator Blockset

-

Fixed-point and floating-point implementation

-

Ready-to-use ControlDesk instruments

Application Areas

The dSPACE XSG Utils Library offers users of real-time FPGA applications enhanced function blocks for implementing their own projects. The library is completely open and can be used in rapid control prototyping (RCP) projects as well as for hardware-in-the-loop (HIL) simulation.

Due to the generic programming, the library can be applied to all freely programmable dSPACE real-time FPGA platforms.

Key Benefits

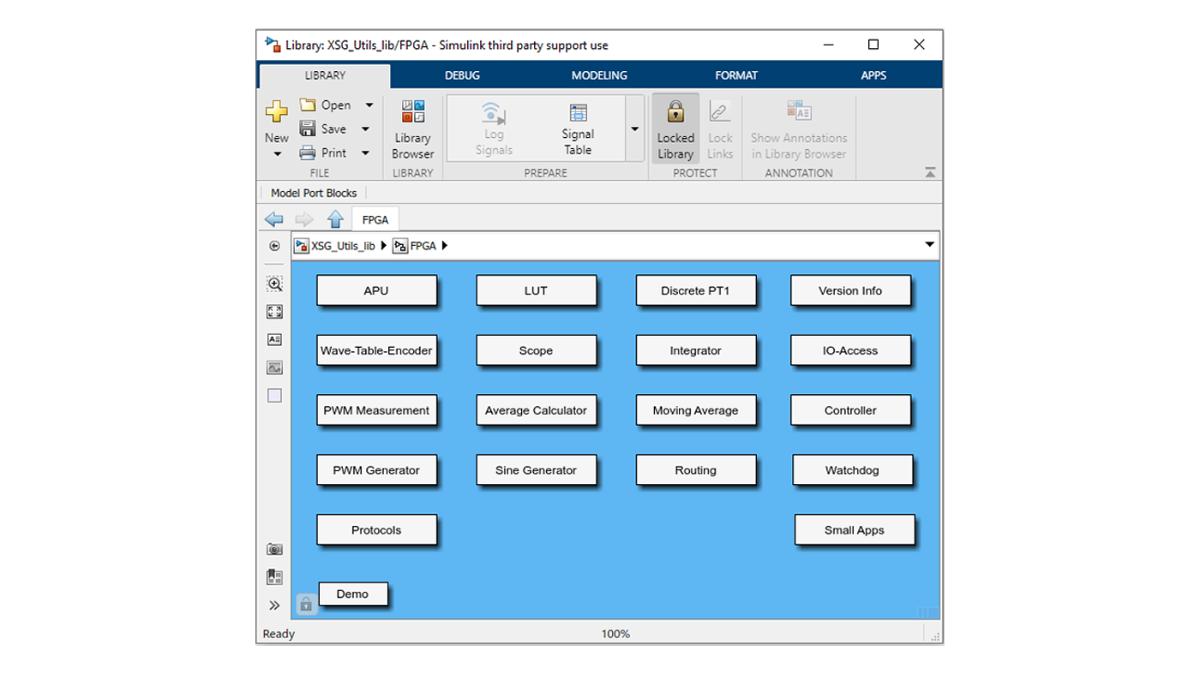

The dSPACE XSG Utils Library contains essential, often needed function blocks for FPGA programming as fixed-point and floating-point implementation. These included blocks provide high quality functions that are available in the standard Simulink library for processor-based implementations. The high-quality function blocks are ready to use and easy to adapt to your project, so they greatly facilitate your FPGA programming. They range from enhanced I/O, scope, and look-up table functions to an average calculator, sine generator, and wavetable encoder.

The XSG Utils Library offers pre-built custom instruments that enable quick access to the most used functions out of ControlDesk (for more information, please see relevant product information).

Task-Specific Versions

The XSG Utils Library is available in two versions:

- XSG Utils Library for developers of FPGA applications to embed their own FPGA real-time models with Xilinx® Vitis™ Model Composer HDL Library, the former Xilinx® System Generator (XSG) Blockset in Simulink®.

- dSPACE XSG Utils Interface Library for linking the preconfigured dSPACE XSG-Utils-based FPGA application with the Simulink-based processor application for data exchange and parameterization.

For comprehensive development projects, both versions are needed.

Available Function Blocks

-

Scope

-

PWM Measurement

-

PWM Generator

-

Look-up Table (1-D, 2-D, and 3-D)

-

I/O Access Functions

-

Integrator

-

PI Controller

-

Average Calculator

-

Sine Generator

-

Discrete PT1

-

Scaling

-

Wavetable Encoder

-

APU

-

UART (RX & TX)

- Small Apps

- Version Info

-

Sine or Cosine

-

Reciprocal

-

Median

-

Three phase PWM generators with three modes: motor control, phase shifted, and user defined

| Functionality | Description |

|---|---|

| Scope | Captures 8 (out of 16) high-frequency signals within the FPGA clock rate and sends the captured data synchronously to the processor, where it can be displayed and stored in instruments such as the ControlDesk plotters. |

| PWM Measurement | Measures the dead time (time between HSD and LSD), high time, and period time of a single-phase or three-phase PWM signal. |

| PWM Generator | Generates an aligned PWM signal (single-phase and three-phase). The dead time and the duty cycle can be configured at runtime. |

| Look-up Table | Configures the accuracy of the table, and the minimum and maximum data values to be covered. Linear interpolation algorithms or the Use Input Below method can be configured online: 1-D, 2-D, and 3-D look-up tables are available. If required, the tables can be updated at runtime. |

| I/O Access Functions | Enables flexible programming and run-time parameterization of the onboard FPGA I/O as well as the stimulus mode. |

- XSG Electric Component Library Plant models of electric drives featuring FPGA-based simulations

- MicroAutoBox II Compact, stand-alone prototyping unit with real-time hardware, I/O, and signal conditioning

Drive innovation forward. Always on the pulse of technology development.

Subscribe to our expert knowledge. Learn from our successful project examples. Keep up to date on simulation and validation. Subscribe to/manage dSPACE direct and aerospace & defense now.